# ANALOG DEVICES

# 64-Position Up/Down Control Digital Potentiometer

# **Preliminary Technical Data**

# AD5227

### FEATURES

- 64-Position

- 10k, 50k, 100kΩ end-to-end terminal resistance

- Simple Up/Down Digital or Manual Configurable Control

- Mid-Scale Preset

- Low Potentiometer Mode TC 10ppm/°C

- Low Rheostat Mode TC 35ppm/°C

- Ultra low power, IDD = 5µA Max

- Fast Adjustment Time, ts = 1µs

- Chip Select Enable Multi-Devices Operation

- Low Operating Voltage, 2.7V to 5.5V

- Automotive Temperature Range -40°C to +105°C

- Compact Thin SOT23-8 (2.9 mm × 3 mm) package

### **APPLICATIONS**

- Mechanical Potentiometers and Trimmers Replacements

- LCD Contrast, Brightness, and Backlight Controls

- Portable Electronics Level Adjustments

- Programmable Power Supply

- Digital Trimmers Replacements

- Automatic Close Loop Control

### **GENERAL DESCRIPTIONS**

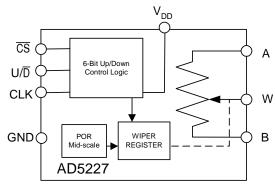

AD5227 is Analog Devices latest 64-Step Up/Down Control Digital Potentiometer<sup>1</sup>. This device performs the same electronic adjustment function as a 5V potentiometer or variable resistor. Its common 3-wire up/down interface allows high-speed as well as low-speed digital controls. AD5227 presets to mid-scale in power up. When  $\overline{CS}$  is enabled, the Up/Down direction is depended on the state of  $U/\overline{D}$  and it executes at every clock pulse. The interface is simple that can be controlled by any host controllers, discrete logics, and manually with rotary encoder or push buttons. AD5227 adequate resolution, small footprint, and simple interface enable it to be the potential replacements of mechanical potentiometers and trimmers with typically 6X improved resolution, solid-state reliability, and design layout flexibility. These enhancements can result in considerable cost saving in end users' systems. The AD5227 is available in compact thin SOT23-8 package. All parts are guaranteed to operate over the extended industrial temperature range of -40°C to +105°C.

For users who consider EEMEM potentiometers, they may refer to some recommendations in the Applications Section.

### FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

#### Table 1. Truth Table

| CS | CLK           | U/D | Operation                                            |

|----|---------------|-----|------------------------------------------------------|

| 0  | $\rightarrow$ | 0   | R <sub>WB</sub> Decrement, R <sub>WA</sub> Increment |

| 0  | $\downarrow$  | 1   | R <sub>WB</sub> Increment, R <sub>WA</sub> Decrement |

| 1  | Х             | Х   | No Operation                                         |

### **PIN CONFIGURATION**

Note

1. The term digital potentiometer and RDAC are used interchangeably.

### REV. Pr F 1/20/2004

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel: 781/329-4700

World Wide Web Site: http://www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2004

## **TABLE OF CONTENTS**

| General DescriptionError! Bookmark not defined.       |

|-------------------------------------------------------|

| AD5227—SpecificationsError! Bookmark not defined.     |

| Absolute Maximum Ratings 5                            |

| Thermal ResistanceError! Bookmark not defined.        |

| Pin Configurations And Functional Descriptions Error! |

| Bookmark not defined.                                 |

|                                                       |

## **REVISION HISTORY**

Revision PrD: Initial Version

| Typical Performance Characteristics Error! Bookmark not |

|---------------------------------------------------------|

| defined.                                                |

| Theory of Operation Error! Bookmark not defined.        |

| Outline Dimensions10                                    |

| ESD Caution10                                           |

### $Table \ 2. \ ELECTRICAL \ CHARACTERISTICS \ 10k \ , \ 50k \ , \ 100k \\ \Omega \ \ VERSION \ (V_{DD} = +3V \pm 10\% \ or \ +5V \pm 10\%, \ V_{A} = +V_{DD}, \ V_{B} = 0V, \ -40^{\circ}C < T_{A} \ C < T$

< +105°C unless otherwise noted.)

| Parameter                                 | Symbol                                   | Conditions                                           | Min  | Typ <sup>1</sup> | Max             | Units              |

|-------------------------------------------|------------------------------------------|------------------------------------------------------|------|------------------|-----------------|--------------------|

| DC CHARACTERISTICS RHEOSTAT N             | 10DE                                     |                                                      |      |                  |                 |                    |

| Resistor Differential NL <sup>2</sup>     | R-DNL                                    | R <sub>WB</sub> , V <sub>A</sub> =NC                 | -1   | ±0.25            | +1              | LSB                |

| Resistor Nonlinearity <sup>2</sup>        | R-INL                                    | R <sub>WB</sub> , V <sub>A</sub> =NC                 |      | ±0.5             | +1              | LSB                |

| Nominal resistor tolerance                | $\Delta R_{AB}/R_{AB}$                   | $T_A = 25^{\circ}C$                                  | -30  |                  | 30              | %                  |

| Resistance Temperature Coefficien         | t (ΔR <sub>AB</sub> /R <sub>AB</sub> )/2 | <u></u> мт                                           |      |                  | 35              | ppm/°C             |

| Wiper Resistance                          | R <sub>W</sub>                           | $I_W = V_{DD}/R$ , $V_{DD} = 5V$                     |      | 120              | 200             | Ω                  |

| Wiper Resistance                          | R <sub>W</sub>                           | $I_{W} = V_{DD} / R, V_{DD} = 2.7V$                  |      | 200              | 400             | Ω                  |

| DC CHARACTERISTICS POTENTIOM              | ETER DIVIDE                              | RMODE                                                |      |                  |                 |                    |

| Resolution                                | N                                        |                                                      |      |                  | 6               | Bits               |

| Integral Nonlinearity <sup>4</sup>        | INL                                      |                                                      | -1   | ±0.5             | +1              | LSB                |

| Differential Nonlinearity <sup>4</sup>    | DNL                                      |                                                      | -1   | ±0.1             | +1              | LSB                |

| Voltage Divider Temperature Coeff         | i¢ient(∆V <sub>w</sub> /V                | v)/∆TMid-scale                                       |      | 5                |                 | ppm/°C             |

| Full-Scale Error                          | V <sub>WFSE</sub>                        | +32 Steps from Mid-scale (Full-scale)                | -2   | -0.5             | +0              | LSB                |

| Zero-Scale Error                          | V <sub>WZSE</sub>                        | -32 Steps from Mid-scale (Zero-scale)                | 0    | +0.5             | +1              | LSB                |

| RESISTOR TERMINALS                        |                                          |                                                      |      |                  |                 |                    |

| Voltage Range <sup>5</sup>                | V <sub>A,B,W</sub>                       |                                                      | 0    |                  | V <sub>DD</sub> | v                  |

| Capacitance <sup>6</sup> A, B             | C <sub>A,B</sub>                         | f = 1 MHz, measured to GND, Mid-scale                |      | 45               | 00              | pF                 |

| Capacitance <sup>6</sup> W                | C <sub>W</sub>                           | f = 1 MHz, measured to GND, Mid-scale                |      | 60               |                 | pF                 |

| Common Mode Leakage                       | ICM                                      | $V_A = V_B = V_W$                                    |      | 1                |                 | nA                 |

| DIGITAL INPUTS & OUTPUTS                  |                                          |                                                      |      |                  |                 |                    |

| Input Logic High                          | VIH                                      | $V_{DD} = +5V$                                       | 2.4  |                  |                 | V                  |

| Input Logic Low                           | V <sub>IL</sub>                          | $V_{DD} = +5V$                                       |      |                  | 0.8             | V                  |

| Input Current                             | I                                        | $V_{IN} = 0V \text{ or } +5V$                        |      |                  | 1               | μA                 |

| Input Capacitance <sup>6</sup>            | C <sub>IL</sub>                          |                                                      |      | 5                |                 | pF                 |

| POWER SUPPLIES                            |                                          |                                                      |      | İ                |                 |                    |

| Power Supply Range                        | V <sub>DD</sub>                          |                                                      | +2.7 |                  | +5.5            | v                  |

| Supply Current                            | I <sub>DD</sub>                          | $V_{IH} = +5V \text{ or } V_{IL} = 0V, V_{DD} = +5V$ |      |                  | 5               | μA                 |

| Power Dissipation <sup>10</sup>           | P <sub>DISS</sub>                        | $V_{IH} = +5V \text{ or } V_{IL} = 0V, V_{DD} = +5V$ |      |                  | 25              | μW                 |

| Power Supply Sensitivity                  | PSS                                      | $\Delta V_{DD} = +5V \pm 10\%$                       |      | 0.05             | 0.15            | μ <b>νν</b><br>%/% |

|                                           |                                          | Δv <sub>DD</sub> - +3v ±10%                          |      | 0.05             | 0.15            | / 70/70            |

| DYNAMIC CHARACTERISTICS <sup>6,9,11</sup> |                                          |                                                      |      |                  |                 |                    |

| Bandwidth – 3dB                           | BW                                       | $R_{AB} = 10k/50k/100k\Omega, Mid-scale$             |      | 600/X/Y          |                 | kHz                |

| Total Harmonic Distortion                 | THD <sub>W</sub>                         | $V_A = 1$ Vrms + 2V dc, $V_B = 2$ V DC, f=1KHz       |      | 0.05             |                 | %                  |

| V <sub>W</sub> Settling Time              | t <sub>S</sub>                           | $V_A = V_{DD}, V_B = 0V, \pm 1$ LSB error band       |      |                  |                 | μs                 |

| Resistor Noise Voltage                    | e <sub>N_WB</sub>                        | $R_{WB} = 5K\Omega, f = 1kHz$                        |      | 14               |                 | nV√Hz              |

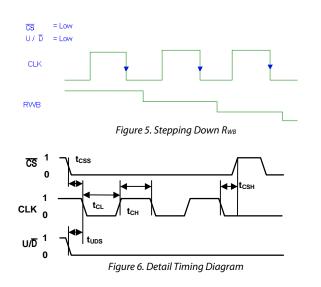

| NTERFACE TIMING CHARACTERIST              |                                          |                                                      |      |                  |                 |                    |

| nput Clock Pulse Width                    | t <sub>CH</sub> ,t <sub>CL</sub>         | Clock level high or low                              | 10   |                  |                 | ns                 |

| CS to CLK Setup Time                      | t <sub>CSS</sub>                         |                                                      | 10   |                  |                 | ns                 |

| CS Rise to CLK Hold Time                  | t <sub>CSH</sub>                         |                                                      | 10   |                  |                 | ns                 |

| U/D to Clock Fall Setup Time              | t <sub>UDS</sub>                         |                                                      | 10   |                  |                 | ns                 |

NOTES:

1. Typicals represent average readings at +25°C,  $V_{DD} = +5V$ .

2. Resistor position nonlinearity error R-INL is the deviation from an ideal value measured between the maximum resistance and the minimum resistance wiper positions. R-DNL measures the relative step change from ideal between successive tap positions. Parts are guaranteed monotonic.

4. INL and DNL are measured at V<sub>w</sub> with the RDAC configured as a potentiometer divider similar to a voltage output D/A converter.  $V_A = V_{DD}$  and  $V_B = 0V$ .

DNL specification limits of ±1LSB maximum are Guaranteed Monotonic operating conditions.

5. Resistor terminals A,B,W have no limitations on polarity with respect to each other.

6. Guaranteed by design and not subject to production test.

7. Measured at the A terminal. The A terminal is open circuited in shutdown mode.

9. Bandwidth, noise and settling time are dependent on the terminal resistance value chosen. The lowest R value results in the fastest settling time and highest bandwidth. The highest R value result in the minimum overall power consumption.

10. P<sub>DISS</sub> is calculated from (I<sub>DD</sub> x V<sub>DD</sub>). CMOS logic level inputs result in minimum power dissipation.

REV. Pr F 1/20/2004

11. 12.

All dynamic characteristics use  $V_{DD} = +5V$ . See timing diagram for location of measured values. All input control voltages are specified with  $t_R = t_F = 1$ ns(10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6V. Switching characteristics are measured using both  $V_{\text{DD}} = +5V$ .

## **Absolute Maximum Ratings**

### Table 3. AD5227 Absolute Maximum Ratings

| Parameter                                                                   | Rating               |

|-----------------------------------------------------------------------------|----------------------|

| V <sub>DD</sub> to GND                                                      | -0.3, +7V            |

| V <sub>A</sub> , V <sub>B</sub> , V <sub>W</sub> to GND                     | GND, V <sub>DD</sub> |

| Maximum Current                                                             |                      |

| I <sub>WB</sub> , I <sub>WA</sub> Pulsed                                    | ±20mA                |

| $I_{WB}$ Continuous ( $R_{WB} \le 1 \text{ k}\Omega$ , A open) <sup>1</sup> | ±5mA                 |

| $I_{WA}$ Continuous ( $R_{WA} \le 1 \text{ k}\Omega$ , B open) <sup>1</sup> | ±5mA                 |

| Digital Input Voltage to GND                                                | 0V, V <sub>DD</sub>  |

| Operating Temperature Range                                                 | -40°C to +105°C      |

| Maximum Junction Temperature (T <sub>J</sub> max)                           | 150°C                |

| Storage Temperature                                                         | -65°C to +150°C      |

| Lead Temperature (Soldering, 10 – 30 sec)                                   | 245°C                |

| Thermal Resistance <sup>2</sup> $\theta_{JA_{r}}$                           | 230°C/W              |

<sup>1</sup>Maximum terminal current is bounded by the maximum applied voltage across any two of the A, B, and W terminals at a given resistance, the maximum current handling of the switches, and the maximum power dissipation of the package.  $V_{DD} = 5$  V.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition s above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Package Power Dissipation = (T<sub>J</sub>MAX – T<sub>A</sub>) /  $\theta_{JA}$

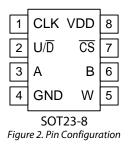

## **Pin Configurations And Functional Descriptions**

| 1 | CLK | VDD                    | 8 |

|---|-----|------------------------|---|

| 2 | U/D | $\overline{\text{CS}}$ | 7 |

| 3 | A   | В                      | 6 |

| 4 | GND | W                      | 5 |

Figure 3. SOT23-8

| Table 4. Pin Function Descriptions |      |                                                                                                                                                                                     |  |  |

|------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin No.                            | Name | Description                                                                                                                                                                         |  |  |

| 1                                  | CLK  | Clock Input. Each Clock Pulse Executes<br>The Step-Up or Step-Down of the<br>Resistances. The Direction is Determined<br>By The State in U/D Pin. Clock is<br>Negative Edge Trigger |  |  |

| 2                                  | U/D  | Up/Down Selections. Logic 1 Selects Up<br>and 0 Selects Down                                                                                                                        |  |  |

| 3                                  | A    | Resistor Terminal A. GND≤V <sub>A</sub> ≤V <sub>DD</sub>                                                                                                                            |  |  |

| 4                                  | GND  | Common Ground                                                                                                                                                                       |  |  |

| 5                                  | W    | Wiper Terminal W. GND≤V <sub>W</sub> ≤V <sub>DD</sub>                                                                                                                               |  |  |

| 6 | В               | Resistor Terminal B. GND≤V <sub>B</sub> ≤V <sub>DD</sub> |

|---|-----------------|----------------------------------------------------------|

| 7 | CS              | Chip Select. Active Low                                  |

| 8 | V <sub>DD</sub> | Positive Power Supply, +2.7 V to +5.5 V                  |

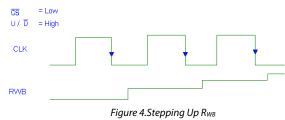

### INTERFACE TIMING DIAGRAM

## **OPERATION**

The AD5227 provides a 64 position digitally-controlled potentiometer device. It presets to a mid-scale at system power ON. When  $\overline{CS}$  is enabled, changing the resistance settings is achieved by clocking the CLK pin. The direction of stepping is controlled by the U/ $\overline{D}$  control input. Additional CLK pulses will not change the wiper setting when the wiper hits the maximum or the minimum setting. When push button switch is used to control the clock, appropriate de-bounce circuitry should be considered. The timing requirements are shown in Figure 6.

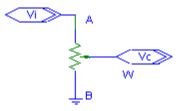

Figure 7. AD5227 Equivalent RDAC Circuit

### PROGRAMMING THE DIGITAL POTENTIOMETERS Rheostat Operation

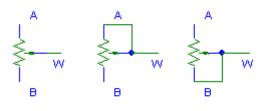

If only the W-to-B or W-to-A terminals are used as variable resistor, the unused terminal can be opened or shorted with W, such operation is called rheostat mode, Figure 8.

Figure 8. Rheostat Mode Configuration

The end-to-end resistance  $R_{AB}$  has 64 contact points accessed by the wiper terminal, plus the B terminal contact if  $R_{WB}$  is used, , see Figure 7. Clocking the CLK input will step  $R_{WB}$  by one step and the direction is determined by the state of  $U/\overline{D}$  pin. In the open loop applications, the change of resistance,  $R_{WB}$  can be determined by the number of clock pulses applied to the clock pin provided its maximum and minimum settings are not reached. The  $R_{WB}$  can therefore be approximated as

$$\Delta R_{WB} = \pm \left( CP \cdot \frac{R_{AB}}{64} + R_W \right) \tag{1}$$

where:

*CP* is the number of clock pulses.

$R_{AB}$  is the end-to-end resistance.

$R_W$  is the wiper resistance contributed by the on-resistance of the internal switch.

Since in the lowest end of the resistor string, a finite wiper resistance of 60 is present. Care should be taken to limit the current flow between W and B in this state to a maximum pulse current of no more than 20 mA. Otherwise, degradation or possible destruction of the internal switch contact can occur.

Similar to the mechanical potentiometer, the resistance of the RDAC between the wiper W and terminal A also produces a digitally controlled complementary resistance  $R_{WA}$ . When these terminals are used, the B-terminal can be opened or shorted to W. The  $R_{WA}$  can also be approximated if its maximum and minimum settings are not reached.

$$\Delta R_{WA} = \pm \left( (64 - CP) \frac{R_{AB}}{64} + R_W \right) \tag{2}$$

Equations 1 and 2 do not apply when CP = 0.

The typical distribution of the resistance tolerance from device to device is process lot dependent and is possible to have  $\pm 30\%$  tolerance.

#### **Potentiometer Mode Operation**

If all three terminals are used, the operation is called the potentiometer mode. The most common configuration is the voltage divider operation, Figure 9.

Figure 9. Potentiometer Mode Configuration

The transfer function is:

$$\Delta V_W = \frac{\frac{CP}{64}R_{AB} + R_W}{R_{AB} + 2R_W}V_A \tag{3}$$

If we ignore the effect of the wiper resistance, the transfer function simplifies to

$$\Delta V_W = \frac{CP}{64} V_A \tag{4}$$

Unlike in rheostat mode operation where the absolute tolerance is high, potentiometer mode operation yields an almost ratio-metric function of CP/64 with a relatively small error contributed by the R<sub>w</sub> terms, the tolerance effect is therefore almost cancelled. Although the thin film step resistor R<sub>s</sub> and CMOS switches resistance R<sub>w</sub> have very different temperature coefficients, the ratio-metric adjustment also makes the overall temperature coefficient effect reduced to 5ppm/°C except at low value codes where R<sub>w</sub> dominates.

Potentiometer mode operations include others operations such as opamp input and feedback resistors network and other voltage scaling applications. A, W, and B terminals can in fact be input or output terminals and have no polarity constraint provided that  $|V_{AB}|$ ,  $|V_{WA}|$ , and  $|V_{WB}|$  do not exceed VDD-to-GND.

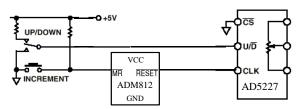

#### INTERFACING

The AD5227 contains a three-wire serial input interface. The three inputs are clock (CLK),  $\overline{CS}$  (Chip Select), and up/down control (U/ $\overline{D}$ ). These inputs can be controlled digitally for optimum speed and flexibility. Standard logic families work well. On the other hand, they can also be controlled by mechanical means for simple manual operation. The states of the  $\overline{CS}$  and U/ $\overline{D}$  can be selected by the mechanical switches. The CLK input can be controlled by a pushbutton but it should be properly debounced by flip-flops or other suitable means. The negative-edge sensitive CLK input requires clean transitions to avoid clocking multiple pulses into the internal UP/Down counter register.

When  $\overline{CS}$  is pulled low, a clock pulse increments or decrements the up/down counter and the direction is determined by the state of

the U/ $\overline{D}$  control pin. When the state of U/ $\overline{D}$  remains, the device continues to change to the same direction under consecutive clocks until it hits the end of the resistance setting.

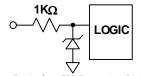

All digital inputs are protected with a series input resistor and parallel Zener ESD structure shown in Figure 10. Applies to digital input pins  $\overline{CS}$ , U/ $\overline{D}$ , and CLK.

Figure 10. Equivalent ESD Protection Digital Pins

### **Terminal Voltage Operation Range**

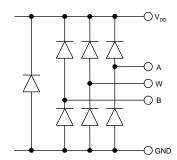

The AD5227 is designed with internal ESD diodes for protection but they also set the boundary of the terminal operating voltages. Positive signals present on terminal A, B, or W that exceeds  $V_{DD}$  will be clamped by the forward biased diode. There is no polarity constraint between  $V_{AB}$ ,  $V_{WA}$ , and  $V_{WB}$  but they cannot be higher than  $V_{DD}$ -to-GND.

Figure 11. Maximum Terminal Voltages Set by V<sub>DD</sub> and GND

#### **Power-Up and Power-Down Sequences**

Since there are ESD protection diodes that limit the voltage compliance at terminals A, B, and W (Figure 11), it is important to power  $V_{DD}$  before applying any voltage to terminals A, B, and W. Otherwise, the diodes will be forward biased such that  $V_{DD}$  will be powered unintentionally and may affect the rest of the users' circuit. Similarly,  $V_{DD}$  should be powered down last. The ideal power-up sequence is in the following order: GND,  $V_{DD}$ , digital inputs, and  $V_{A/B/W}$ . The order of powering  $V_A$ ,  $V_B$ ,  $V_W$ , and digital inputs is not important as long as they are powered after  $V_{DD}$ .

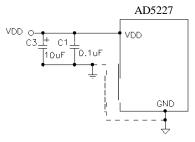

### Layout and Power Supply Biasing

It is always a good practice to employ compact, minimum lead length layout design. The leads to the input should be as direct as possible with a minimum conductor length. Ground paths should have low resistance and low inductance.

Similarly, it is also good practice to bypass the power supplies with quality capacitors. Low ESR (Equivalent Series Resistance) 1 $\mu$ F to 10 $\mu$ F tantalum or electrolytic capacitors should be applied at the

supplies to minimize any transient disturbance and filter low frequency ripple. Figure 12 illustrates the basic supply-bypassing configuration for the AD5227

Figure 12. Power Supply Bypassing

The ground pin of the AD5227 is a digital ground reference. To minimize the digital ground bounce, the AD5227 ground terminal should be joined remotely to the common ground ground, Figure 12

# AD5227

## **APPLICATIONS**

### Manual Control with Push Button and Toggle Switch

Figure 13. Manual Push Button Up/Down Control

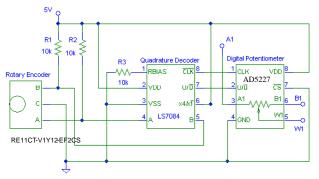

### **Manual Control with Rotary Encorder**

#### **Simple Automatic Controller** R3 +5\ 2.2 VDD 504 R4 P1 741 8132 4 иD U4 68u NDS0610 GNE f=1/(R8\*C4) AD5227 D1 White LED U2 AD8605 U1 AD5273 100k

Figure 15. Automatic Controller Implemented in white LED driver

Figure 15 shows a simple automatic close loop controller that can be used in many different applications. The core of the controller consists of a one time programmable digital pot, a comparator, a 6bit up/down control digital pot, and a Schmitt trigger NAND gate. For illustration purpose, the application shows a conceptual linear control of white LED. Typical white LEDs employ PWM controls for efficiency purpose but the circuit above can be expanded to PWM with an addition of a boost regulator. In the factory calibration, the one time programmable<sup>1</sup> digital pot AD5273 is used to adjust various intensity levels. Once the desirable level is determined, a computer program can program such setting permanently and the system can be shipped to the field.

When the system is powered up, we may assume the white LED remains at off due to the delay. The photocell sensor senses no intensity and therefore provides high output resistance. The comparator -IN node becomes high and outputs low if this level is higher than the +IN reference level and makes the up/down control digital pot select to the count down direction. AD5227 will decrement at every clock pulse generated by the clock generator U4, R3, and C1. The continued lowering of P1's gate voltage makes it turn on harder to drive the white LED. The operation reverses when the white LED intensity is higher than the reference level. This system is therefore self-regulated. Although the resolution is limited to  $\pm 1.6\%$ , this system is a simple self-contained close loop control and is adaptive if U1 is made adjustable at the field

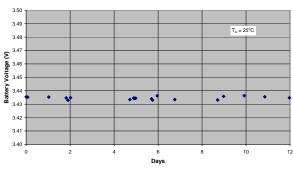

### **Constant Bias To Retain Resistance Setting**

For users who consider EEMEM pots but cannot justify the additional cost for their designs, they may consider AD5227 as low cost alternatives. They may constantly bias the AD5227 with the supply to retain the resistance setting. AD5227 is designed specifically with low power in mind that allows power conservation even in the battery-operated systems. As shown in Figure 16, a similar low power digital pot is applied in a 3.4V 450mAhour Li-ion cellphone battery. The measurement shows that the device drains negligible power. Constantly bias the pot is not an impractical approach because most of the portable devices nowadays do not require detachable batteries for charging purpose. Although the resistance setting of AD5227 will be lost when the battery needs replacement, such event occurs infrequently that such inconvenience is justified for most applications. And when it happens, user should be provided with a mean to adjust the setting accordingly.

Figure 16. Battery Consumption Measurement.

## AD5227

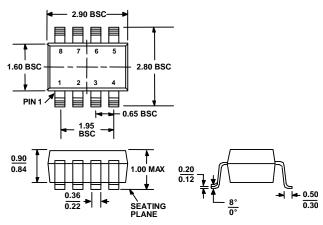

## **Outline Dimensions**

Dimensions shown in inches and (mm)

*Figure 17.* 8-Lead Small Outline Transistor Package [Thin SOT-23] (UJ-8) Dimensions shown in millimeters

## ESD Caution

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

| Tab | le | 1. Ordering Guide |  |

|-----|----|-------------------|--|

|     | -  |                   |  |

| Model <sup>1</sup> | R <sub>AB</sub> (kΩ) | Temp Range      | Package Code | Package<br>Description | Full Container<br>Quantity | Brand |

|--------------------|----------------------|-----------------|--------------|------------------------|----------------------------|-------|

| AD5227BUJZ10-R7    | 10                   | -40°C to +105°C | UJ           | SOT23-8                | 3000                       | D3G   |

| AD5227BUJZ10       | 10                   | -40°C to +105°C | UJ           | SOT23-8                | 250                        | D3G   |

| AD5227BUJZ50-R7    | 50                   | -40°C to +105°C | IJ           | SOT23-8                | 3000                       | D3H   |

| AD5227BUJZ50       | 50                   | -40°C to +105°C | UJ           | SOT23-8                | 250                        | D3H   |

| AD5227BUJZ100-R7   | 100                  | -40°C to +105°C | UJ           | SOT23-8                | 3000                       | D3J   |

| AD5227BUJZ100      | 100                  | -40°C to +105°C | UJ           | SOT23-8                | 250                        | D3J   |

| AD5227EVAL         | 10                   |                 |              |                        | 1                          |       |

1. Z=Pb Free Parts

The end-to-end resistance RAB is available in  $10k\Omega$ ,  $50k\Omega$ , and  $100k\Omega$ . The final three characters of the part number determine the nominal resistance value, e.g.,  $10k\Omega = 10$ .